für SC12 (SC13)

Um eine herkömmliche IDE Festplatte an den SC12/SC13 anzuschließen, wird ein 8/16 Bit Interface benötigt. Der SC12/SC13 hat aber nur einen 8-Bit Datenbus nach außen geführt. Glücklicherweise muß für das IDE Interface nur das erste, das Datenregister, als 16 Bit Register mit externer Logik emuliert werden. Die übrigen Register sind nur 8 Bit breit. Der Zugriff auf das 16 Bit Register oder die restlichen 8 Bitregister werden über die Adressleitungen auskodiert. Die etwas umfangreichere Logik habe ich deshalb mit VHDL und einem CPLD realisiert.

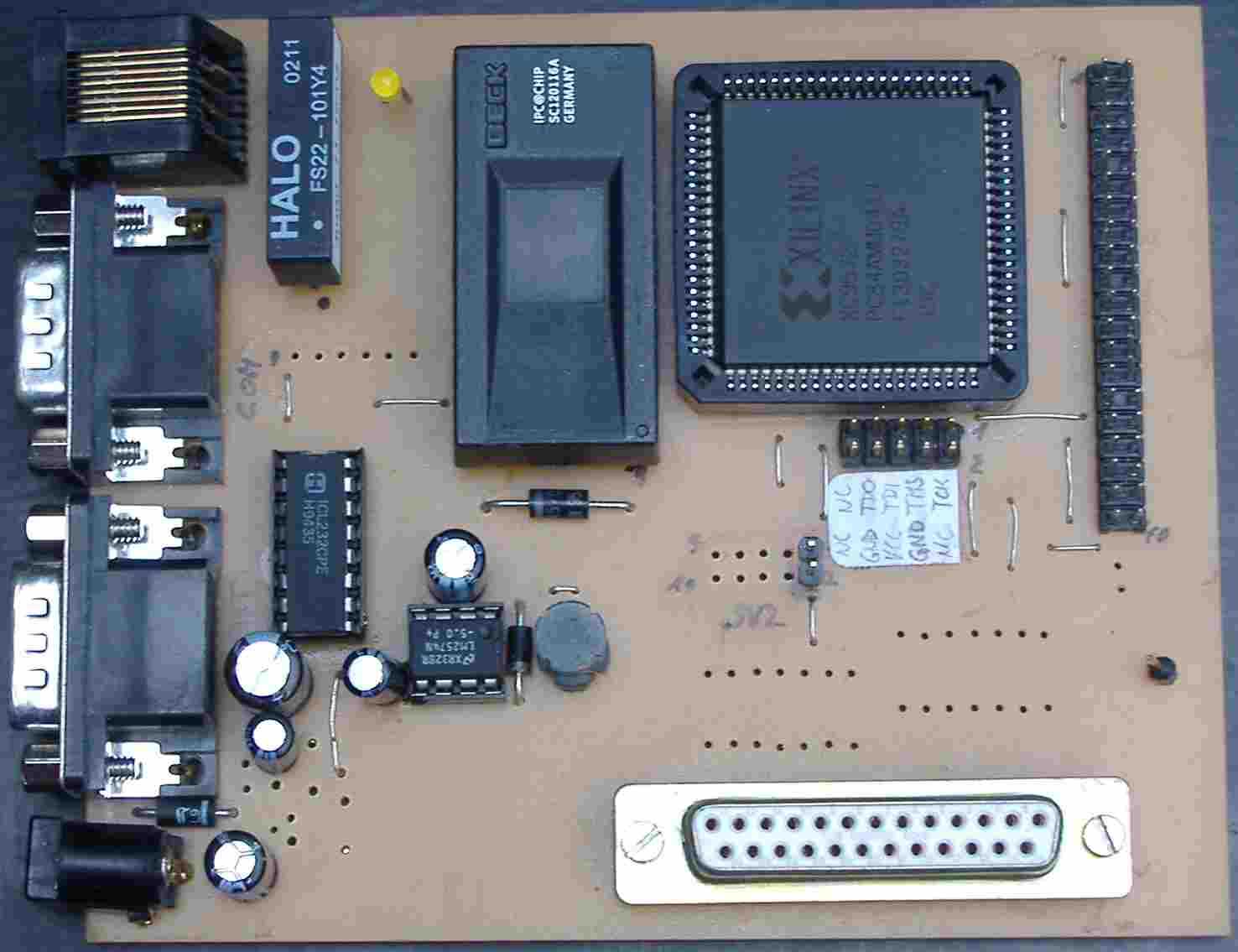

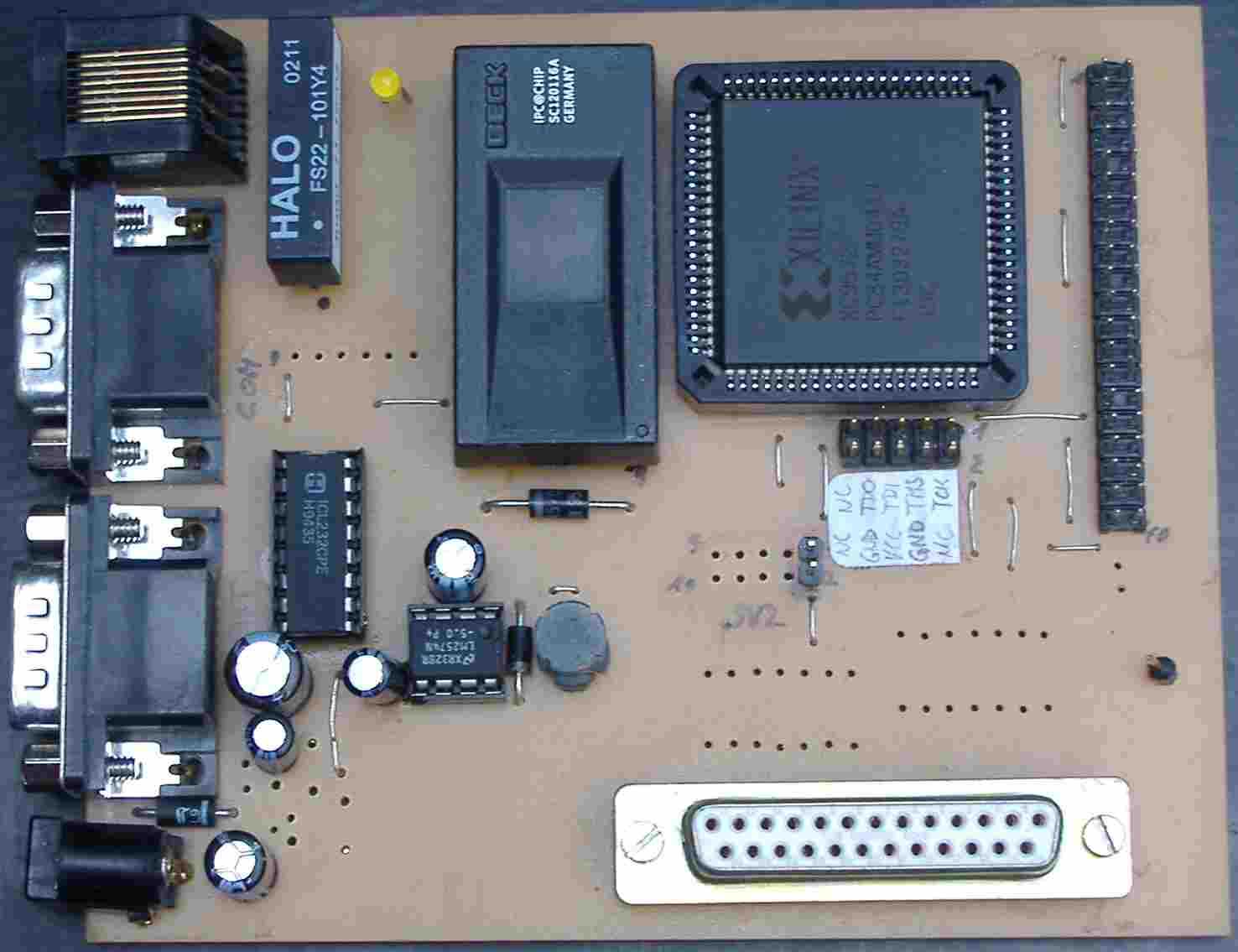

Zur Programmierung des CPLD ist in der Schaltung noch das "parallel cable 3" mit untergebracht. (Hier auf der Platine außer dem DSUB-Stecker nicht bestückt). Möglich ist auch eine Programmierung des CPLD direkt über PIO-Leitungen des SC12/SC13 möglich und folgt in Kürze. Die passende Software habe ich schon am DK60 erfolgreich getestet. Statt dem 84 Pin CPLD kann auch ein 44 Pin CPLD verwendet werden.

Abgebildet ist die erste Version der Platine. In dem neuen Layout ist, neben der 8..30V Spannungsversorgung auch noch eine 5V Versorgung mit einem PC-Netzteilstecker vorgesehen. Das macht die Verkabelung der Spannungsversorgung praktischer.

Die Festplatte wird über den standart Beck EXTIDE-Treiber in das RTOS eingebunden.

Einstellungen für den EXTIDE-Treiber (define.h) :

Databus = DATABUS_16

ALE = used

CE0 = 0x620

CE1 = 0x630

Die nutzbare Partitionsgröße wird durch das RTOS auf 2GB begrenzt.

PDF Schaltplam: 16Bit_IDE.pdf

XILINX VHDL: HD16_xilinx.zip